Hiện nay, các mô hình sư phạm ( của nước ngoài chứ Vietnam chắc chưa có ) dạy thế này : lấy một miếng Silicon, bào ra một ít, pha tạp với một ít phosphorous ( phốt pho ), phủ lên một miếng chip, pha tạp thêm mốt ít silicon với Boron ( nguyên tố thứ 5 trong bảng tuần hoàn hóa học ), và cho một ít kim loại vào giữa tất cả mọi thứ. Đó là mô hình cơ bản đến một cách kì lạ về cách làm việc của các nhà máy vật liệu bán dẫn, nhưng nó không sai lạc dữ dội cho lắm. Kết luận mà mọi người rút ra sau khi học được điều này là : Những con chip đó là các thiết bị ba chiều. Nhưng các lớp là cực kì nhỏ, và độ dày tổng cộng của các lớp hoạt động của một con chip còn nhỏ hơn độ dày một sơi tóc của con người. Một chút nghiên cứu và suy nghĩ là bạn có thể nhận ra cấu trúc của một mạch tích hợp 3 chiều không phải là “3 chiều”.

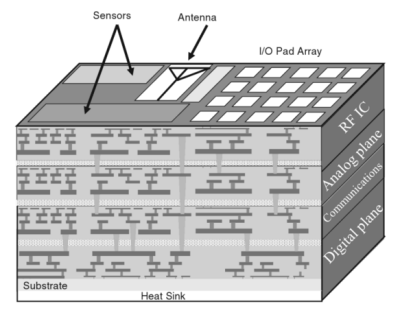

Gần đây, các lời đồn thổi và những suy đoán đến từ những người làm trong mảng điện tử đã dẫn dắt dư luận về các chip 3 chiều như là tương lai của ngành công nghiệp silicon. Những con chip này không dày vài lớp như ví dụ ở đầu bài. Thay vì sử dụng vài tá lớp mạch điện, 100 hay thậm chí nhiều lớp transistor hơn sẽ được gắng vào 1 mảnh silicon. Lý do cho sự thay đổi này là do mục tiêu rút ngắn đường đi của tín hiêu, giảm điện trở (dẫn đến giảm nhiệt), và tối ưu hiệu năng cũng như công suất trong một thiết kế.

Các ý tưởng ảnh hưởng đến việc tạp ra các chip 3 chiều hiện này không phải là mới, các khái niệm này đã xuất hiện ngay từ buổi đầu của ngành công nghiệp bán dẫn. Cái mới chính là cách mà các thiết bị này được mang đến với thị trường, những thách thức mà hiện nay Intel và các công ty vật liệu bán dẫn khác đang phải đối đối mặt, và ý nghĩa của nó trong vài năm sau khi một thế hệ chip được tung ra.

Lịch sử của chip 3D

Vào cuối những năm 1960 và đầu những năm 1970, chip ngày càng phức tạp. Mặt trước của công nghệ bán dẫn chuyển từ op-amps và các gói tín hiệu số nhỏ sang vật liệu bán dẫn với hang ngàn transistor. Và với sự thay đổi này làm tăng độ tin cậy và khả năng kết nối giữa các phần khác nhau của một con chip.

Trong sự phát triển công nghệ suốt 50 năm qua, transistor đã thay đổi từ một thứ mà chúng ta có thể nhìn bằng mắt thường thành một thứ có bề ngang chỉ vài phân tử. Sự liên kết (interconnection) trở thành một lựa chọn hiển nhiên, đặt biệt với sự gia tăng liên tuc của độ phức tạp trong thiết kế, gia tăng độ rộng BUS, và nhiều ngõ vào/ra hơn.

Với những yêu cầu cao hơn liên tục được đặt cho một con chip (vốn dĩ tồn tại trong thế giới 3 chiều của chúng ta), câu trả lời rõ ràng nhất về việc đặt các liên kết này ở đâu cũng chính là câu trả lời lời cho các thành phố của chúng ta ngày này. Nếu bạn không thể “ĐI RA” nữa, thì bạn hãy “ĐI LÊN”.

Sự nghiên cứu này diễn ra liên tục trong suốt những năm 1970 cho đến những năm 1990 như là một cuộc theo đuổi hàn lâm, với giải pháp cho một vấn đề mới. Làm thế nào để bạn làm mát bên trong một khối lập phương ( gồm rất nhiều con chip ) ? Bạn cho hệ thống làm mát đi bên trong khối lập phương ấy, đi xuyên suốt các con chip. Vấn đề này có vẻ đơn giản, và giải pháp có thể giải thích rất dễ dàng, tuy nhiên để hiện thực hóa giải pháp này lại là một vấn đề hết sức đau đầu. Một giải pháp dễ hơn để tăng mật độ các transistor là chồng các “package” lên nhau.

Chip chính trong Raspberry Pi Zero thật ra là 2 con IC. Phía dưới là bộ xử lý ARM và phía trên là DRAM. Đây chính là cấu trúc “Package on Package” (POP)

Các thiết bị POP này có thể được tìm thấy – có thể hơi khó khăn một chút – ở hàng tá thiết bị. Con chip lớn của Raspberry Pi Zero, Model A, và Model B là các thiết bị POP, với RAM ở chip trên, kết nối trực tiếp với Broadcom CPU. Hiện nay, loại RAM có dung lượng cao nhất và mới nhất cũng sử dụng công nghệ này. POP chính là giải pháp và các công ty hướng đến cho vấn đề liên kết.

Trạng thái hiện tại của chip 3D

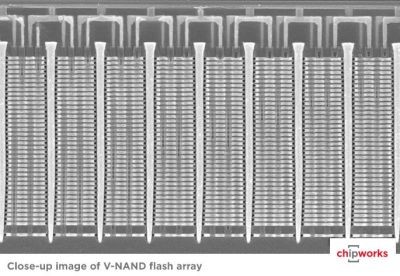

Mặc dù ý tương chip 3D với nhiều lớp silicon chỉ là ý tưởng cũ, gần đây chúng ta thấy công nghệ này đang được đưa vào các thiết bị tiêu dung. Vào năm 2013, Samsung tiến vào thị trường 3D flash (bộ nhớ flash) với công nghệ V-NAND, và được xem là công nghệ transistor 3D thực sự đầu tiên được sản xuất.

Chipwork thực sự là một sự quá sức của Samsung V-NAND trong dòng sản phẩm 850 pro SSD. Bằng bất cứ nghĩa nào thì đó thực sự là một nỗ lực thiết kế đáng kinh ngạc. Mô hình V-NAND xếp chồng trong sản phẩm SSD này là 38 lớp transistor được xếp chống lên nhau, với mỗi transistor giữ một bit thong tin.

Sự đột phá này rõ ràng cho phép Samsun đặt nhiều transistor hơn ở cùng một diện tích nhỏ đưa đến hiệu năng cao hơn. Nếu bạn tin vào các mẫu quảng cáo của Samsung, có lẽ 100 lớp transistor cũng có thể nhét vừa vào một con chip, lót đường cho các ổ cứng với dung lượng cực kì, cực kì lớn. Dung lượng không chỉ là lợi ích duy nhất; nhờ vào cấu trúc của V-NAND, nhiễu giữa các tế bào bộ nhớ (memory cell) cũng được giảm, làm tăng hiệu suất xủa ổ cứng. Độ bền ghi – số lần một tế bào bộ nhớ có thể được ghi lại mà không bị hỏng – được cải thiện hơn so với các bộ nhớ Flash 2D NAND bình thường.

Tất nhiên, mặc dù hầu hết các tuyên bố của Samsung về bộ nhớ flash V-NAND 3D đều là chiêu trò marketing, bạn không thể phủ nhận sản phẩm SSD này của Samsung cũng rất tốt. Có thể bạn sẽ đặt ra một câu hỏi “khi nào thì chúng ta sẽ có những thứ khác ngoài SSD?”

Thế hệ kế tiếp của Nvidia GPU, Volta, sẽ sử dụng các DRAM xếp chồng khi được tung ra vào năm 2018. Mặc dù độ phức tạp sẽ chỉ tương đương bộ nhớ Flash NAND, điều này cũng cho chúng ta thấy chip 3D đang dần trở nên phổ biến, và chỉ còn là vấn đề thời gian trước khi chúng ta nghĩ tới một CPU như là một thiết bị 3D thực sự, mà không phải chỉ là vài lớp xếp chồng lên nhau.

3D CPU

Nếu bạn có dõi theo nguồn gốc của các thành tựu công nghệ thú vị trong lĩnh vực bán dẫn, những bước tiến thường bắt đầu từ các trường đại học, đến các ngành sản xuất bộ nhớ, và cuối cùng là chất kết dính để giữ các CPU lại với nhau. Cho đến lúc, Intel nổi tiếng vì chip Dram hiệu năng rất cao của họ (hàng trăm byte), trước khi được biết đến khi chuyển sang sản xuất CPU.

Như vậy bạn cũng dễ thấy CPU với thiết kế nhiều lớp không phải mục tiêu quá xa. Đối với Intel, bước tiến lớn kế tiếp sẽ là EMIB (Embedded Multi-die Interconnect Bridge), dùng mô hình PoP, phủ epoxy, và thực hiện mọi thứ ở cấp độ thấp hơn. EMIB là mặt phẳng chính giữa các lớp. Bằng cách đặt nhiều lớp trên một mảnh silicon, với các đường dẫn hình zig-zag, Intel có thể đặt nhiều mạch khác nhau trên cùng một mảnh silicon .

Mặc dù giải pháp này sẽ là chiêu bài mới của Intel, nó không thực sự là một chip 3D. Chúng ta sẽ còn phải đợi thêm một thời gian nữa; chúng ta mới chỉ có bộ nhớ Flash 3D, và 3D Ram vẫn chưa được tung ra trong một vài năm nữa. Sản xuất 3D CPU sẽ là một thử thách thiết kế phức tạp hơn rất nhiều, do vậy, có thể chúng ta sẽ phải đợi đâu đó một thập kỉ nữa.

Chắc chắn chip 3D sẽ được ra đời. Chỉ là vấn đề về thời gian. Đơn giản chỉ là vì không còn cách nào khác để tăng mật độ các liên kết, tăng số lượng thiết bị trên một con chip, hay tăng tốc độ.

Cách duy nhất chính là tiến vào chiều thứ 3 của silicon.

Technicalvn Kỹ Thuật Việt Nam

Technicalvn Kỹ Thuật Việt Nam